L'illusion de l'espace infini

Au cœur de la mémoire virtuelle se trouve une illusion : l'illusion de posséder plus de mémoire qu'il n'en existe physiquement. Mais comment fonctionne ce tour de magie ?

Entrée : Les tables de pages

Les tables de pages sont les héros méconnus de la gestion de la mémoire. Elles agissent comme une carte, traduisant l'immensité des adresses virtuelles en le domaine limité de la mémoire physique. Voici une vue simplifiée de leur fonctionnement :

struct PageTableEntry {

uint32_t physical_page_number : 20;

uint32_t present : 1;

uint32_t writable : 1;

uint32_t user_accessible : 1;

uint32_t write_through : 1;

uint32_t cache_disabled : 1;

uint32_t accessed : 1;

uint32_t dirty : 1;

uint32_t reserved : 5;

};

Chaque entrée dans la table de pages correspond à une page en mémoire virtuelle, généralement de 4 Ko. Lorsqu'un programme tente d'accéder à la mémoire, le CPU utilise la table de pages pour savoir où cette mémoire se trouve réellement dans la RAM physique.

Le coût de la traduction

Mais voici le hic : traduire les adresses via les tables de pages est lent. Vraiment lent. On parle de lenteur comparable à "regarder la peinture sécher". Pour chaque accès mémoire, le CPU devrait effectuer plusieurs recherches en mémoire juste pour déterminer où se trouve réellement les données. C'est là que notre prochain acteur entre en jeu...

TLB : Les démons de la vitesse de la traduction d'adresses

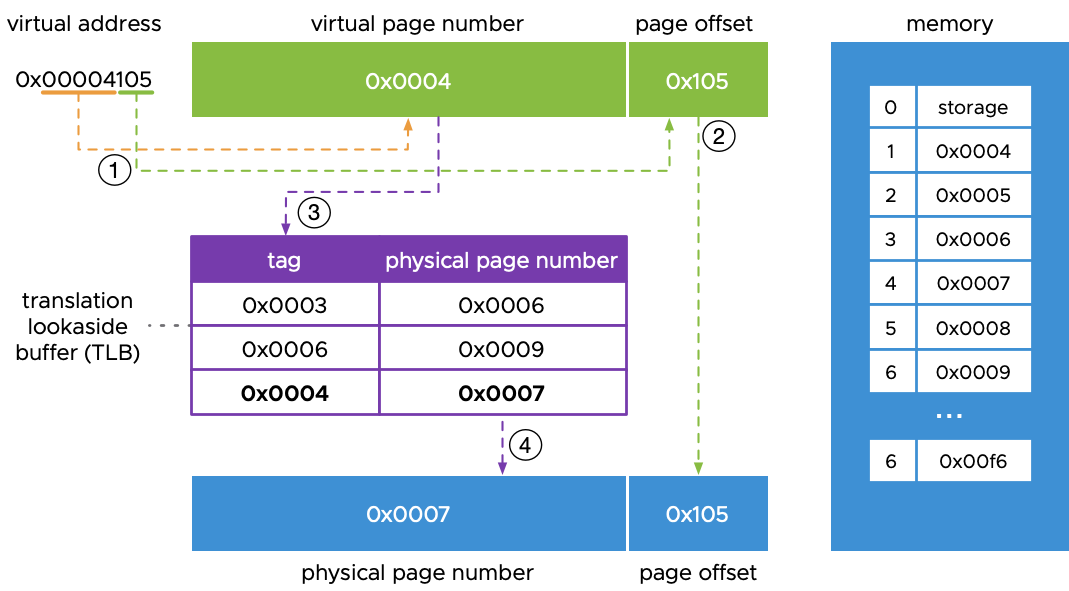

Les Translation Lookaside Buffers, ou TLB, sont le nitro de notre moteur de mémoire virtuelle. Ce sont de petites caches rapides qui stockent les traductions récentes des adresses virtuelles en adresses physiques.

Pensez aux TLB comme à la mémoire à court terme de votre cerveau pour les directions. Au lieu de sortir une carte (table de pages) chaque fois que vous voulez aller quelque part, vous vous souvenez simplement de l'itinéraire si vous y êtes allé récemment.

Comment les TLB opèrent leur magie

Voici un pseudocode simplifié de la façon dont un TLB pourrait fonctionner :

def access_memory(virtual_address):

if virtual_address in TLB:

physical_address = TLB[virtual_address]

return fetch_data(physical_address)

else:

physical_address = page_table_lookup(virtual_address)

TLB[virtual_address] = physical_address

return fetch_data(physical_address)

Ce mécanisme simple accélère considérablement l'accès à la mémoire. En fait, les CPU modernes peuvent avoir des taux de réussite de plus de 99 % sur leurs TLB, ce qui signifie que 99 accès mémoire sur 100 n'ont pas besoin de toucher les tables de pages lentes du tout !

Le côté obscur : Les ratés de TLB et le thrashing

Mais que se passe-t-il lorsque le TLB ne trouve pas une traduction ? C'est ce qu'on appelle un raté de TLB, et c'est aussi amusant que de trouver un bug dans le code de production à 16h59 un vendredi.

Lorsqu'un raté de TLB se produit, le CPU doit :

- Parcourir les tables de pages pour trouver la bonne traduction

- Mettre à jour le TLB avec la nouvelle traduction

- Réessayer l'accès à la mémoire

Ce processus peut être douloureusement lent, surtout s'il se produit fréquemment. Lorsque votre programme commence à subir beaucoup de ratés de TLB, les performances peuvent chuter plus vite qu'un ballon de plomb. Cette condition est connue sous le nom de thrashing de TLB, et c'est le cauchemar des applications sensibles aux performances.

Éviter le thrashing

Pour que vos programmes fonctionnent sans accroc, considérez ces conseils :

- Utilisez des tailles de pages plus grandes lorsque c'est approprié (pages énormes sous Linux, grandes pages sous Windows)

- Optimisez vos schémas d'accès à la mémoire pour la localité

- Soyez attentif à la taille de votre ensemble de travail

Rappelez-vous : un TLB heureux est un programme performant !

Au-delà des bases : Techniques avancées de mémoire virtuelle

En nous aventurant plus profondément dans le terrier du lapin de la mémoire virtuelle, nous rencontrons des techniques avancées fascinantes :

Tables de pages inversées

Les tables de pages traditionnelles peuvent consommer beaucoup de mémoire, surtout dans les systèmes 64 bits. Les tables de pages inversées renversent la situation, utilisant une table de hachage pour mapper les pages physiques aux adresses virtuelles. Cela peut réduire considérablement la surcharge mémoire des tables de pages, au prix de temps de recherche potentiellement plus longs.

Tables de pages à plusieurs niveaux

Pour gérer les vastes espaces d'adresses des systèmes modernes, les tables de pages à plusieurs niveaux décomposent le processus de traduction en étapes. Par exemple, un système x86-64 typique pourrait utiliser quatre niveaux de tables de pages :

CR3 → PML4 → PDP → PD → PT → Page Physique

Cette approche hiérarchique permet une utilisation efficace de la mémoire et une gestion flexible de la mémoire.

ASID : Changement de contexte sans vidage

Les Identifiants d'Espace d'Adresse (ASID) sont une astuce ingénieuse utilisée par certaines architectures pour éviter de vider le TLB à chaque changement de contexte. En étiquetant les entrées du TLB avec un ASID, le CPU peut conserver les traductions de plusieurs processus dans le TLB simultanément.

struct TLBEntry {

uint64_t virtual_page_number;

uint64_t physical_page_number;

uint16_t asid;

// ... autres indicateurs

};

Cela peut améliorer considérablement les performances dans les systèmes avec des changements de contexte fréquents.

L'avenir de la mémoire virtuelle

Alors que nous repoussons les limites de l'informatique, la mémoire virtuelle continue d'évoluer. Parmi les développements passionnants à l'horizon, on trouve :

- Gestion de la mémoire hétérogène : Avec l'essor des systèmes combinant différents types de mémoire (DRAM, NVRAM, HBM), les systèmes de mémoire virtuelle s'adaptent pour gérer efficacement ces ressources diverses.

- Promenades de table de pages assistées par le matériel : Certains CPU modernes incluent du matériel dédié pour parcourir les tables de pages, réduisant encore l'impact des ratés de TLB sur les performances.

- Prédiction par apprentissage automatique : Les chercheurs explorent l'utilisation de techniques d'apprentissage automatique pour prédire les schémas d'accès à la mémoire et précharger les pages dans le TLB.

Conclusion : L'épine dorsale invisible de l'informatique moderne

La mémoire virtuelle, avec sa danse complexe de tables de pages et de TLB, forme l'épine dorsale invisible de l'informatique moderne. C'est un témoignage de l'ingéniosité des informaticiens et des ingénieurs, créant l'illusion de vastes espaces mémoire contigus à partir de ressources physiques fragmentées.

La prochaine fois que votre programme s'exécute, ayez une pensée pour la machinerie complexe qui travaille en coulisses, traduisant vos adresses virtuelles insouciantes en réalité physique. Et rappelez-vous, dans le monde de la mémoire virtuelle, rien n'est tout à fait ce qu'il semble être – mais c'est précisément ce qui la rend si puissante.

"En informatique, nous nous tenons sur les épaules de géants – et ces géants se tiennent sur une implémentation très astucieuse de la mémoire virtuelle." - Anonyme Bit Wrangler

Maintenant, allez de l'avant et allouez de la mémoire avec un abandon insouciant – votre système de mémoire virtuelle vous soutient !